ARTIKES-7 FPGA

Papan Inti

AC7A200

Sistem ing Modul

Manual pangguna

Versi Rekam

| Versi | Tanggal | Rilis Miturut | Katrangan |

| Rev 1.0 | 28-06-20 | Rachel Zhou | Rilis pisanan |

Part 1: AC7A200 Papan inti Pambuka

AC7A200 (model papan inti, padha ing ngisor iki) Papan inti FPGA, adhedhasar seri ARTIX-7 XILINX 100T XC7A200T-2FBG484I. Iku papan inti kinerja dhuwur karo kacepetan dhuwur, bandwidth dhuwur lan kapasitas dhuwur. Cocog kanggo komunikasi data kanthi kacepetan dhuwur, pangolahan gambar video, akuisisi data kanthi kacepetan dhuwur, lsp.

Papan inti AC7A200 iki nggunakake rong chip MICRON MT41J256M16HA-125 DDR3, saben DDR nduweni kapasitas 4Gbit; loro Kripik DDR digabungake menyang 32-dicokot data bus jembaré, lan maca / nulis bandwidth data antarane FPGA lan DDR3 nganti 25Gb; konfigurasi kuwi bisa nyukupi kabutuhan Processing data bandwidth dhuwur.

Papan inti AC7A200 ngembangake 180 port IO standar level 3.3V, 15 port IO standar level 1.5V, lan 4 pasangan sinyal diferensial RX/TX kacepetan dhuwur GTP. Kanggo pangguna sing butuh akeh IO, papan inti iki bakal dadi pilihan sing apik. Menapa malih, nuntun antarane chip FPGA lan antarmuka padha dawa lan Processing diferensial, lan ukuran Papan inti mung 2.36 inch * 2.36 inch, kang cocok banget kanggo pembangunan secondary.

Gambar 1-1: Papan Inti AC7A200 (Ngarep View)

Gambar 1-2: Papan Inti AC7A200 (Mburi View)

Bagean 2: Chip FPGA

Kaya kasebut ing ndhuwur, model FPGA sing digunakake yaiku XC7A200T-2FBG484I, sing kalebu seri Artix-7 Xilinx. Kelas kacepetan yaiku 2, lan kelas suhu minangka kelas industri. Model iki minangka paket FGG484 kanthi 484 pin. Xilinx ARTIX-7 FPGA aturan jeneng chip minangka ngisor

Gambar 2-1: Definisi Model Chip Spesifik saka Seri ARTIX-7

Gambar 2-2: chip FPGA ing papan

Paramèter utama chip FPGA XC7A200T minangka nderek

| jeneng | Parameter khusus |

| Sel Logika | 215360 |

| irisan-irisan | 16-02-92 |

| CLB sandal jepit | 269200 |

| Blok RAM (kb) | 13140 |

| DSP irisan | 740 |

| PCIe Gen2 | 1 |

| XADC | 1 XADC, 12bit, 1Mbps AD |

| GTP Transceiver | 4 GTP, maks. 6.6Gb/s |

| Kelas Kacepetan | -2 |

| Kelas Suhu | Industri |

Sistem sumber daya FPGA

Sumber daya FPGA Artix-7 yaiku VCCINT, VCCBRAM, VCCAUX, VCCO, VMGTAVCC lan VMGTAVTT. VCCINT minangka pin sumber daya inti FPGA, sing kudu disambungake menyang 1.0V; VCCBRAM punika pin sumber daya saka FPGA Block RAM, nyambung menyang 1.0V; VCCAUX minangka pin sumber daya tambahan FPGA, nyambungake 1.8V; VCCO punika voltage saben BANK FPGA, kalebu BANK0, BANK13~16, BANK34~35. Ing papan inti FPGA AC7A200, BANK34 lan BANK35 kudu disambungake menyang DDR3, voltage sambungan BANK punika 1.5V, lan voltage saka BANK liyane 3.3V. VCCO saka BANK15 lan BANK16 powered by LDO, lan bisa diganti dening ngganti chip LDO. VMGTAVCC minangka sumber voltage saka transceiver GTP internal FPGA, disambungake menyang 1.0V; VMGTAVTT punika voltage saka transceiver GTP, disambungake menyang 1.2V.

Sistem FPGA Artix-7 mbutuhake urutan power-up dadi daya dening VCCINT, banjur VCCBRAM, banjur VCCAUX, lan pungkasane VCCO. Yen VCCINT lan VCCBRAM duwe vol padhatage, padha bisa powered munggah ing wektu sing padha. Urutan daya outages diwalik. Urutan power-up saka transceiver GTP yaiku VCCINT, banjur VMGTAVCC, banjur VMGTAVTT. Yen VCCINT lan VMGTAVCC duwe volume sing padhatage, padha bisa powered munggah ing wektu sing padha. Urutan power-off mung kebalikan saka urutan power-on.

Bagean 3: Crystal Diferensial Aktif

Papan inti AC7A200 dilengkapi karo loro kristal diferensial aktif Sitime, siji yaiku 200MHz, model yaiku SiT9102-200.00MHz, jam utama sistem kanggo FPGA lan digunakake kanggo ngasilake jam kontrol DDR3; liyane 125MHz, model SiT9102 -125MHz, referensi input jam kanggo transceiver GTP.

Bagean 3.1: Jam Diferensial Aktif 200Mhz

G1 ing Figure 3-1 punika 200M kristal diferensial aktif sing nyedhiyani Papan pembangunan sumber jam sistem. Output kristal disambungake menyang pin jam global BANK34 MRCC (R4 lan T4) saka FPGA. Jam diferensial 200Mhz iki bisa digunakake kanggo nyopir logika pangguna ing FPGA. Pangguna bisa ngatur PLLs lan DCMs nang FPGA kanggo generate jam saka frekuensi beda.

Gambar 3-1: Skema Kristal Diferensial Aktif 200Mhz

Gambar 3-2: Kristal Diferensial Aktif 200Mhz ing Papan Inti

200Mhz Diferensial Jam Pin Assignment

| Jeneng Sinyal | PIN FPGA |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

Bagean 3.2: 125MHz Active Differential Crystal

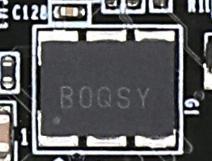

G2 ing Figure 3-3 punika kristal diferensial aktif 125MHz, kang jam input referensi kasedhiya kanggo modul GTP nang FPGA. Output kristal disambungake menyang pin jam GTP BANK216 MGTREFCLK0P (F6) lan MGTREFCLK0N (E6) saka FPGA.

Gambar 3-3: Skema Kristal Diferensial Aktif 125MHz

Gambar 3-4: Kristal Diferensial Aktif 125MHz ing Papan Inti

Assignment Pin Jam Diferensial 125MHz

| Jeneng Net | PIN FPGA |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

Part 4: DDR3 DRAM

Papan inti FPGA AC7A200 dilengkapi karo rong chip Micron 4Gbit (512MB) DDR3 (8Gbit total), model MT41J256M16HA-125 (kompatibel karo MT41K256M16HA-125). DDR3 SDRAM nduweni kacepetan operasi maksimum 400MHz (data rate 800Mbps). Sistem memori DDR3 langsung disambungake menyang antarmuka memori saka BANK 34 lan BANK35 saka FPGA. Konfigurasi tartamtu saka DDR3 SDRAM kapacak ing Tabel 4-1.

| Nomer Bit | Model Chip | Kapasitas | Pabrik |

| U5,U6 | MT41J256M16HA-125 | 256M x 16 bit | Mikron |

Tabel 4-1: Konfigurasi DDR3 SDRAM

Desain hardware DDR3 mbutuhake pertimbangan ketat integritas sinyal. Kita wis kebak dianggep resistor cocog / resistance terminal, tilak kontrol impedansi, lan tilak kontrol dawa ing desain sirkuit lan desain PCB kanggo mesthekake dhuwur-kacepetan lan operasi stabil saka DDR3. Gambar 4-1 rincian sambungan hardware DDR3 DRAM

Gambar 4-1: Skema DDR3 DRAM

Figure 4-2: DDR3 ing Papan inti

Tugas pin DRAM DDR3:

| Jeneng Net | Jeneng PIN FPGA | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [1] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [2] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [3] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [4] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [5] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [6] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [7] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [8] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [9] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [10] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [11] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [12] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [13] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [14] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [15] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [16] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [17] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [18] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [19] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [20] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [21] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [22] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [23] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [24] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [25] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [26] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [27] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [28] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [29] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [30] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [31] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | AA4 |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | AA5 |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | AA3 |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | AA1 |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_RESET | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

Bagean 5: QSPI Flash

Papan inti FPGA AC7A200 dilengkapi siji 128Mbit QSPI FLASH, lan model yaiku N25Q128, sing nggunakake 3.3V CMOS voltage standar. Amarga sifat non-molah malih saka QSPI FLASH, bisa digunakake minangka piranti boot kanggo sistem kanggo nyimpen gambar boot saka sistem. Gambar kasebut utamane kalebu bit FPGA files, kode aplikasi ARM, kode aplikasi inti alus lan data pangguna liyane files. Model spesifik lan paramèter sing gegandhengan karo SPI FLASH ditampilake ing Tabel 5-1.

| posisi | Model | Kapasitas | Pabrik |

| U8 | N25Q128 | 128M Bit | Numonyx |

Tabel 5-1: Spesifikasi QSPI FLASH

QSPI FLASH disambungake menyang pin khusus BANK0 lan BANK14 saka chip FPGA. Pin jam disambungake menyang CCLK0 saka BANK0, lan data liyane lan sinyal chip pilih disambungake menyang D00 ~ D03 lan pin FCS saka BANK14. Gambar 5-1 nuduhake sambungan hardware QSPI Flash.

Gambar 5-1: Skema Flash QSPI

Tugas pin Flash QSPI:

| Jeneng Net | Jeneng PIN FPGA | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

Gambar 5-2: QSPI FLASH ing Papan Inti

Part 6: Lampu LED ing Papan Inti

Ana 3 lampu LED abang ing papan inti AC7A200 FPGA, salah sijine yaiku lampu indikator daya (PWR), siji yaiku lampu LED konfigurasi (DONE), lan siji yaiku lampu LED pangguna. Nalika Papan inti powered, indikator daya bakal madhangi; nalika FPGA diatur, konfigurasi LED bakal madhangi. Lampu LED pangguna disambungake menyang IO BANK34, pangguna bisa ngontrol lan mateni lampu kanthi program kasebut. Nalika IO voltage disambungake menyang pangguna LED dhuwur, pangguna LED madhangi. Nalika sambungan IO voltage kurang, LED pangguna bakal dipateni. Diagram skematik sambungan hardware lampu LED ditampilake ing Gambar 6-1:

Gambar 6-1: Lampu LED ing Skema Papan Inti

Gambar 6-2: Lampu LED ing Papan Inti

Panganggo LEDs Pin Assignment

| Jeneng Sinyal | Jeneng Pin FPGA | Nomer Pin FPGA | Katrangan |

| LED1 | IO_L15N_T2_DQS_34 | W5 | Pangguna LED |

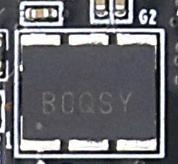

Bagian 7: JTAG Antarmuka

Ing JTAG soket test J1 dilindhungi undhang-undhang ing papan inti AC7A200 kanggo JTAG download lan debugging nalika Papan inti digunakake piyambak. Gambar 7-1 minangka bagean skema saka JTAG port, kang melu TMS, TDI, TDO, TCK. , GND, +3.3V enem sinyal iki.

Gambar 7-1: JTAG Skema Antarmuka

Ing JTAG antarmuka J1 ing AC7A200 Papan inti FPGA nggunakake 6-pin 2.54mm pitch single-row test bolongan. Yen sampeyan kudu nggunakake JTAG konektor kanggo debug ing Papan inti, sampeyan kudu solder 6-pin single-baris pin header.

Gambar 7-2 nuduhake JTAG antarmuka J1 ing Papan inti AC7A200 FPGA.

Gambar 7-2 JTAG Antarmuka ing Papan Inti

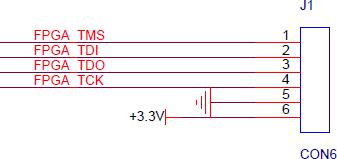

Bagean 8: Antarmuka Daya ing Papan Inti

Supaya Papan inti AC7A200 FPGA bisa digunakake piyambak, Papan inti dilindhungi undhang-undhang 2-pin antarmuka sumber daya J2. Yen pangguna pengin debug fungsi papan inti kanthi kapisah (tanpa papan operator), piranti eksternal kudu nyedhiyakake +5V kanggo nyuplai daya menyang papan inti.

Gambar 8-1: Skema Antarmuka Daya ing Papan Inti

Gambar 8-2: Antarmuka daya ing Papan Inti

Part 9: Papan kanggo Papan Konektor pin assignment

Papan inti wis total papat Papan-kacepetan dhuwur kanggo konektor Papan.

Papan inti nggunakake papat konektor antar-papan 80-pin kanggo nyambung menyang papan operator. Port IO saka FPGA disambungake menyang papat konektor kanthi nuntun diferensial. Jarak pin konektor yaiku 0.5mm, lebokake menyang papan menyang konektor papan ing papan operator kanggo komunikasi data kanthi kacepetan dhuwur.

Papan kanggo Papan Konektor CON1

Papan 80-pin kanggo konektor Papan CON1, kang digunakake kanggo nyambungake karo sumber daya VCCIN (+ 5V) lan lemah ing Papan operator, ngluwihi IOs normal saka FPGA. Sampeyan kudu nyatet kene sing 15 pin CON1 disambungake menyang port IO saka BANK34, amarga sambungan BANK34 disambungake menyang DDR3. Mulane, voltage standar kabeh IOs BANK34 iki 1.5V.

Pin Assignment saka Papan kanggo Papan Konektor CON1

| CON1 PIN |

Net jeneng |

FPGA PIN |

Voltage tingkat |

CON1 PIN |

Net jeneng |

FPGA PIN |

Voltage tingkat |

| PIN 1 | VCCIN | – | +5V | PIN 2 | VCCIN | – | +5V |

| PIN 3 | VCCIN | – | +5V | PIN 4 | VCCIN | – | +5V |

| PIN 5 | VCCIN | – | +5V | PIN 6 | VCCIN | – | +5V |

| PIN 7 | VCCIN | – | +5V | PIN 8 | VCCIN | – | +5V |

| PIN 9 | GND | – | lemah | PIN 10 | GND | – | lemah |

| PIN 11 | NC | – | NC | PIN 12 | NC | – | NC |

| PIN 13 | NC | – | NC | PIN 14 | NC | – | NC |

| PIN 15 | NC | – | NC | PIN 16 | B13_L4_P | AA15 | 3.3V |

| PIN 17 | NC | – | NC | PIN 18 | B13_L4_N | AB15 | 3.3V |

| PIN 19 | GND | – | lemah | PIN 20 | GND | – | lemah |

| PIN 21 | B13_L5_P | Y13 | 3.3V | PIN 22 | B13_L1_P | Y16 | 3.3V |

| PIN 23 | B13_L5_N | AA14 | 3.3V | PIN 24 | B13_L1_N | AA16 | 3.3V |

| PIN 25 | B13_L7_P | AB11 | 3.3V | PIN 26 | B13_L2_P | AB16 | 3.3V |

| PIN 27 | B13_L7_P | AB12 | 3.3V | PIN 28 | B13_L2_N | AB17 | 3.3V |

| PIN 29 | GND | – | lemah | PIN 30 | GND | – | lemah |

| PIN 31 | B13_L3_P | AA13 | 3.3V | PIN 32 | B13_L6_P | W14 | 3.3V |

| PIN 33 | B13_L3_N | AB13 | 3.3V | PIN 34 | B13_L6_N | Y14 | 3.3V |

| PIN 35 | B34_L23_P | Y8 | 1.5V | PIN 36 | B34_L20_P | AB7 | 1.5V |

| PIN 37 | B34_L23_N | Y7 | 1.5V | PIN 38 | B34_L20_N | AB6 | 1.5V |

| PIN 39 | GND | – | lemah | PIN 40 | GND | – | lemah |

| PIN 41 | B34_L18_N | AA6 | 1.5V | PIN 42 | B34_L21_N | V8 | 1.5V |

| PIN 43 | B34_L18_P | Y6 | 1.5V | PIN 44 | B34_L21_P | V9 | 1.5V |

| PIN 45 | B34_L19_P | V7 | 1.5V | PIN 46 | B34_L22_P | AA8 | 1.5V |

| PIN 47 | B34_L19_N | W7 | 1.5V | PIN 48 | B34_L22_N | AB8 | 1.5V |

| PIN 49 | GND | – | lemah | PIN 50 | GND | – | lemah |

| PIN 51 | XADC_VN | M9 | Analog | PIN 52 | NC | ||

| PIN 53 | XADC_VP | L10 | Analog | PIN 54 | B34_L25 | U7 | 1.5V |

| PIN 55 | NC | – | NC | PIN 56 | B34_L24_P | W9 | 1.5V |

| PIN 57 | NC | – | NC | PIN 58 | B34_L24_N | Y9 | 1.5V |

| PIN 59 | GND | – | lemah | PIN 60 | GND | – | lemah |

| PIN 61 | B16_L1_N | F14 | 3.3V | PIN 62 | NC | – | NC |

| PIN 63 | B16_L1_P | F13 | 3.3V | PIN 64 | NC | – | NC |

| PIN 65 | B16_L4_N | E14 | 3.3V | PIN 66 | NC | – | NC |

| PIN 67 | B16_L4_P | E13 | 3.3V | PIN 68 | NC | – | NC |

| PIN 69 | GND | – | lemah | PIN 70 | GND | – | lemah |

| PIN 71 | B16_L6_N | D15 | 3.3V | PIN 72 | NC | – | NC |

| PIN 73 | B16_L6_P | D14 | 3.3V | PIN 74 | NC | – | NC |

| PIN 75 | B16_L8_P | C13 | 3.3V | PIN 76 | NC | – | NC |

| PIN 77 | B16_L8_N | B13 | 3.3V | PIN 78 | NC | – | NC |

| PIN 79 | NC | – | NC | PIN 80 | NC | – | NC |

Gambar 9-1: Konektor Papan kanggo Papan CON1 ing Papan Inti

Papan kanggo Papan Konektor CON2

Header sambungan wadon 80-pin CON2 digunakake kanggo ngluwihi IO normal saka BANK13 lan BANK14 saka FPGA. Voltage standar loro BANK punika 3.3V.

Pin Assignment saka Papan kanggo Papan Konektor CON2

| CON2 PIN |

Net jeneng |

FPGA PIN |

Voltage tingkat |

CON2 PIN |

Net jeneng |

FPGA PIN |

Voltage tingkat |

| PIN 1 | B13_L16_P | W15 | 3.3V | PIN 2 | B14_L16_P | V17 | 3.3V |

| PIN 3 | B13_L16_N | W16 | 3.3V | PIN 4 | B14_L16_N | W17 | 3.3V |

| PIN 5 | B13_L15_P | T14 | 3.3V | PIN 6 | B13_L14_P | U15 | 3.3V |

| PIN 7 | B13_L15_N | T15 | 3.3V | PIN 8 | B13_L14_N | V15 | 3.3V |

| PIN 9 | GND | – | lemah | PIN 10 | GND | – | lemah |

| PIN 11 | B13_L13_P | V13 | 3.3V | PIN 12 | B14_L10_P | AB21 | 3.3V |

| PIN 13 | B13_L13_N | V14 | 3.3V | PIN 14 | B14_L10_N | AB22 | 3.3V |

| PIN 15 | B13_L12_P | W11 | 3.3V | PIN 16 | B14_L8_N | AA21 | 3.3V |

| PIN 17 | B13_L12_N | W12 | 3.3V | PIN 18 | B14_L8_P | AA20 | 3.3V |

| PIN 19 | GND | – | lemah | PIN 20 | GND | – | lemah |

| PIN 21 | B13_L11_P | Y11 | 3.3V | PIN 22 | B14_L15_N | AB20 | 3.3V |

| PIN 23 | B13_L11_N | Y12 | 3.3V | PIN 24 | B14_L15_P | AA19 | 3.3V |

| PIN 25 | B13_L10_P | V10 | 3.3V | PIN 26 | B14_L17_P | AA18 | 3.3V |

| PIN 27 | B13_L10_N | W10 | 3.3V | PIN 28 | B14_L17_N | AB18 | 3.3V |

| PIN 29 | GND | – | lemah | PIN 30 | GND | – | lemah |

| PIN 31 | B13_L9_N | AA11 | 3.3V | PIN 32 | B14_L6_N | T20 | 3.3V |

| PIN 33 | B13_L9_P | AA10 | 3.3V | PIN 34 | B13_IO0 | Y17 | 3.3V |

| PIN 35 | B13_L8_N | AB10 | 3.3V | PIN 36 | B14_L7_N | W22 | 3.3V |

| PIN 37 | B13_L8_P | AA9 | 3.3V | PIN 38 | B14_L7_P | W21 | 3.3V |

| PIN 39 | GND | – | lemah | PIN 40 | GND | – | lemah |

| PIN 41 | B14_L11_N | V20 | 3.3V | PIN 42 | B14_L4_P | T21 | 3.3V |

| PIN 43 | B14_L11_P | U20 | 3.3V | PIN 44 | B14_L4_N | U21 | 3.3V |

| PIN 45 | B14_L14_N | V19 | 3.3V | PIN 46 | B14_L9_P | Y21 | 3.3V |

| PIN 47 | B14_L14_P | V18 | 3.3V | PIN 48 | B14_L9_N | Y22 | 3.3V |

| PIN 49 | GND | – | lemah | PIN 50 | GND | – | lemah |

| PIN 51 | B14_L5_N | R19 | 3.3V | PIN 52 | B14_L12_N | W20 | 3.3V |

| PIN 53 | B14_L5_P | P19 | 3.3V | PIN 54 | B14_L12_P | W19 | 3.3V |

| PIN 55 | B14_L18_N | U18 | 3.3V | PIN 56 | B14_L13_N | Y19 | 3.3V |

| PIN 57 | B14_L18_P | U17 | 3.3V | PIN 58 | B14_L13_P | Y18 | 3.3V |

| PIN 59 | GND | – | lemah | PIN 60 | GND | – | lemah |

| PIN 61 | B13_L17_P | T16 | 3.3V | PIN 62 | B14_L3_N | V22 | 3.3V |

| PIN 63 | B13_L17_N | U16 | 3.3V | PIN 64 | B14_L3_P | U22 | 3.3V |

| PIN 65 | B14_L21_N | P17 | 3.3V | PIN 66 | B14_L20_N | T18 | 3.3V |

| PIN 67 | B14_L21_P | N17 | 3.3V | PIN 68 | B14_L20_P | R18 | 3.3V |

| PIN 69 | GND | – | lemah | PIN 70 | GND | – | lemah |

| PIN 71 | B14_L22_P | P15 | 3.3V | PIN 72 | B14_L19_N | R14 | 3.3V |

| PIN 73 | B14_L22_N | R16 | 3.3V | PIN 74 | B14_L19_P | P14 | 3.3V |

| PIN 75 | B14_L24_N | R17 | 3.3V | PIN 76 | B14_L23_P | N13 | 3.3V |

| PIN 77 | B14_L24_P | P16 | 3.3V | PIN 78 | B14_L23_N | N14 | 3.3V |

| PIN 79 | B14_IO0 | P20 | 3.3V | PIN 80 | B14_IO25 | N15 | 3.3V |

Gambar 9-2: Konektor Papan kanggo Papan CON2 ing Papan Inti

Papan kanggo Papan Konektor CON3

80-pin konektor CON3 digunakake kanggo ngluwihi IO normal saka BANK15 lan BANK16 saka FPGA. Kajaba iku, papat JTAG sinyal uga disambungake menyang Papan operator liwat konektor CON3. Voltage standar BANK15 lan BANK16 bisa diatur dening chip LDO. LDO sing diinstal standar yaiku 3.3V. Yen sampeyan pengin output tingkat standar liyane, sampeyan bisa ngganti karo LDO cocok.

Pin Assignment saka Papan kanggo Papan Konektor CON3

| CON3 PIN |

Net jeneng |

FPGA PIN |

Voltage tingkat |

CON3 PIN |

Net jeneng |

FPGA PIN |

Voltage tingkat |

| PIN 1 | B15_IO0 | J16 | 3.3V | PIN 2 | B15_IO25 | M17 | 3.3V |

| PIN 3 | B16_IO0 | F15 | 3.3V | PIN 4 | B16_IO25 | F21 | 3.3V |

| PIN 5 | B15_L4_P | G17 | 3.3V | PIN 6 | B16_L21_N | A21 | 3.3V |

| PIN 7 | B15_L4_N | G18 | 3.3V | PIN 8 | B16_L21_P | B21 | 3.3V |

| PIN 9 | GND | – | lemah | PIN 10 | GND | – | lemah |

| PIN 11 | B15_L2_P | G15 | 3.3V | PIN 12 | B16_L23_P | E21 | 3.3V |

| PIN 13 | B15_L2_N | G16 | 3.3V | PIN 14 | B16_L23_N | D21 | 3.3V |

| PIN 15 | B15_L12_P | J19 | 3.3V | PIN 16 | B16_L22_P | E22 | 3.3V |

| PIN 17 | B15_L12_N | H19 | 3.3V | PIN 18 | B16_L22_N | D22 | 3.3V |

| PIN 19 | GND | – | lemah | PIN 20 | GND | – | lemah |

| PIN 21 | B15_L11_P | J20 | 3.3V | PIN 22 | B16_L24_P | G21 | 3.3V |

| PIN 23 | B15_L11_N | J21 | 3.3V | PIN 24 | B16_L24_N | G22 | 3.3V |

| PIN 25 | B15_L1_N | G13 | 3.3V | PIN 26 | B15_L8_N | G20 | 3.3V |

| PIN 27 | B15_L1_P | H13 | 3.3V | PIN 28 | B15_L8_P | H20 | 3.3V |

| PIN 29 | GND | – | lemah | PIN 30 | GND | – | lemah |

| PIN 31 | B15_L5_P | J15 | 3.3V | PIN 32 | B15_L7_N | H22 | 3.3V |

| PIN 33 | B15_L5_N | H15 | 3.3V | PIN 34 | B15_L7_P | J22 | 3.3V |

| PIN 35 | B15_L3_N | H14 | 3.3V | PIN 36 | B15_L9_P | K21 | 3.3V |

| PIN 37 | B15_L3_P | J14 | 3.3V | PIN 38 | B15_L9_N | K22 | 3.3V |

| PIN 39 | GND | – | lemah | PIN 40 | GND | – | lemah |

| PIN 41 | B15_L19_P | K13 | 3.3V | PIN 42 | B15_L15_N | M22 | 3.3V |

| PIN 43 | B15_L19_N | K14 | 3.3V | PIN 44 | B15_L15_P | N22 | 3.3V |

| PIN 45 | B15_L20_P | M13 | 3.3V | PIN 46 | B15_L6_N | H18 | 3.3V |

| PIN 47 | B15_L20_N | L13 | 3.3V | PIN 48 | B15_L6_P | H17 | 3.3V |

| PIN 49 | GND | – | lemah | PIN 50 | GND | – | lemah |

| PIN 51 | B15_L14_P | L19 | 3.3V | PIN 52 | B15_L13_N | K19 | 3.3V |

| PIN 53 | B15_L14_N | L20 | 3.3V | PIN 54 | B15_L13_P | K18 | 3.3V |

| PIN 55 | B15_L21_P | K17 | 3.3V | PIN 56 | B15_L10_P | M21 | 3.3V |

| PIN 57 | B15_L21_N | J17 | 3.3V | PIN 58 | B15_L10_N | L21 | 3.3V |

| PIN 59 | GND | – | lemah | PIN 60 | GND | – | lemah |

| PIN 61 | B15_L23_P | L16 | 3.3V | PIN 62 | B15_L18_P | N20 | 3.3V |

| PIN 63 | B15_L23_N | K16 | 3.3V | PIN 64 | B15_L18_N | M20 | 3.3V |

| PIN 65 | B15_L22_P | L14 | 3.3V | PIN 66 | B15_L17_N | N19 | 3.3V |

| PIN 67 | B15_L22_N | L15 | 3.3V | PIN 68 | B15_L17_P | N18 | 3.3V |

| PIN 69 | GND | – | lemah | PIN 70 | GND | – | lemah |

| PIN 71 | B15_L24_P | M15 | 3.3V | PIN 72 | B15_L16_P | M18 | 3.3V |

| PIN 73 | B15_L24_N | M16 | 3.3V | PIN 74 | B15_L16_N | L18 | 3.3V |

| PIN 75 | NC | – | PIN 76 | NC | – | ||

| PIN 77 | FPGA_TCK | V12 | 3.3V | PIN 78 | FPGA_TDI | R13 | 3.3V |

| PIN 79 | FPGA_TDO | U13 | 3.3V | PIN 80 | FPGA_TMS | T13 | 3.3V |

Gambar 9-3: Konektor Papan kanggo Papan CON3 ing Papan Inti

Papan kanggo Papan Konektor CON4

Konektor 80-Pin CON4 digunakake kanggo ngluwihi IO lan GTP data kacepetan dhuwur normal lan sinyal jam saka FPGA BANK16. Voltage standar port IO saka BANK16 bisa diatur dening chip LDO. LDO sing diinstal standar yaiku 3.3V. Yen pangguna pengin output tingkat standar liyane, bisa diganti dening LDO cocok. Data-kacepetan dhuwur lan sinyal jam saka GTP strictly diferensial routed ing Papan inti. Garis data padha dawa lan disimpen ing interval tartamtu kanggo nyegah gangguan sinyal.

Pin Assignment saka Papan kanggo Papan Konektor CON4

| CON4 PIN |

Net jeneng |

FPGA PIN |

Voltage tingkat |

CON4 PIN |

Net jeneng |

FPGA PIN |

Voltage tingkat |

| PIN 1 | NC | – | – | PIN 2 | – | – | |

| PIN 3 | NC | – | – | PIN 4 | – | – | |

| PIN 5 | NC | – | – | PIN 6 | – | – | |

| PIN 7 | NC | – | – | PIN 8 | – | – | |

| PIN 9 | GND | – | lemah | PIN 10 | GND | – | lemah |

| PIN 11 | NC | – | – | PIN 12 | MGT_TX2_P | B6 | Bedane |

| PIN 13 | NC | – | – | PIN 14 | MGT_TX2_N | A6 | Bedane |

| PIN 15 | GND | – | lemah | PIN 16 | GND | – | lemah |

| PIN 17 | MGT_TX3_P | D7 | Bedane | PIN 18 | MGT_RX2_P | B10 | Bedane |

| PIN 19 | MGT_TX3_N | C7 | Bedane | PIN 20 | MGT_RX2_N | A10 | Bedane |

| PIN 21 | GND | – | lemah | PIN 22 | GND | – | lemah |

| PIN 23 | MGT_RX3_P | D9 | Bedane | PIN 24 | MGT_TX0_P | B4 | Bedane |

| PIN 25 | MGT_RX3_N | C9 | Bedane | PIN 26 | MGT_TX0_N | A4 | Bedane |

| PIN 27 | GND | – | lemah | PIN 28 | GND | – | lemah |

| PIN 29 | MGT_TX1_P | D5 | Bedane | PIN 30 | MGT_RX0_P | B8 | Bedane |

| PIN 31 | MGT_TX1_N | C5 | Bedane | PIN 32 | MGT_RX0_N | A8 | Bedane |

| PIN 33 | GND | – | lemah | PIN 34 | GND | – | lemah |

| PIN 35 | MGT_RX1_P | D11 | Bedane | PIN 36 | MGT_CLK1_P | F10 | Bedane |

| PIN 37 | MGT_RX1_N | C11 | Bedane | PIN 38 | MGT_CLK1_N | E10 | Bedane |

| PIN 39 | GND | – | lemah | PIN 40 | GND | – | lemah |

| PIN 41 | B16_L5_P | E16 | 3.3V | PIN 42 | B16_L2_P | F16 | 3.3V |

| PIN 43 | B16_L5_N | D16 | 3.3V | PIN 44 | B16_L2_N | E17 | 3.3V |

| PIN 45 | B16_L7_P | B15 | 3.3V | PIN 46 | B16_L3_P | C14 | 3.3V |

| PIN 47 | B16_L7_N | B16 | 3.3V | PIN 48 | B16_L3_N | C15 | 3.3V |

| PIN 49 | GND | – | lemah | PIN 50 | GND | – | lemah |

| PIN 51 | B16_L9_P | A15 | 3.3V | PIN 52 | B16_L10_P | A13 | 3.3V |

| PIN 53 | B16_L9_N | A16 | 3.3V | PIN 54 | B16_L10_N | A14 | 3.3V |

| PIN 55 | B16_L11_P | B17 | 3.3V | PIN 56 | B16_L12_P | D17 | 3.3V |

| PIN 57 | B16_L11_N | B18 | 3.3V | PIN 58 | B16_L12_N | C17 | 3.3V |

| PIN 59 | GND | – | lemah | PIN 60 | GND | – | lemah |

| PIN 61 | B16_L13_P | C18 | 3.3V | PIN 62 | B16_L14_P | E19 | 3.3V |

| PIN 63 | B16_L13_N | C19 | 3.3V | PIN 64 | B16_L14_N | D19 | 3.3V |

| PIN 65 | B16_L15_P | F18 | 3.3V | PIN 66 | B16_L16_P | B20 | 3.3V |

| PIN 67 | B16_L15_N | E18 | 3.3V | PIN 68 | B16_L16_N | A20 | 3.3V |

| PIN 69 | GND | – | lemah | PIN 70 | GND | – | lemah |

| PIN 71 | B16_L17_P | A18 | 3.3V | PIN 72 | B16_L18_P | F19 | 3.3V |

| PIN 73 | B16_L17_N | A19 | 3.3V | PIN 74 | B16_L18_N | F20 | 3.3V |

| PIN 75 | B16_L19_P | D20 | 3.3V | PIN 76 | B16_L20_P | C22 | 3.3V |

| PIN 77 | B16_L19_N | C20 | 3.3V | PIN 78 | B16_L20_N | B22 | 3.3V |

| PIN 79 | NC | – | PIN 80 | NC | – |

Gambar 9-4: Konektor Papan kanggo Papan CON4 ing Papan Inti

Bagean 10: Sumber Daya

Papan inti AC7A200 FPGA didhukung dening DC5V liwat papan operator, lan didhukung dening antarmuka USB Mini nalika digunakake piyambak. Ati-ati supaya ora nyuplai daya kanthi Mini USB lan papan operator bebarengan kanggo nyegah karusakan. Diagram desain sumber daya ing Papan ditampilake ing Figure 10-1.

Gambar 10-1: Pasokan Daya ing skema papan inti

Papan inti powered dening + 5V lan diowahi kanggo + 3.3V, + 1.5V, + 1.8V, + 1.0V papat-cara sumber daya liwat telung DC / DC power supply chip TLV62130RGT. Saiki +1.0V bisa nganti 6A, lan telung arus output liyane bisa nganti 3A. VCCIO digawe dening siji LDOSPX3819M5-3-3. VCCIO utamané nyuplai daya kanggo BANK15 lan BANK16 saka FPGA. Pangguna bisa ngganti IO saka BANK15,16 kanggo vol bedatage standar dening ngganti chip LDO sing. 1.5V ngasilake VTT lan VREF voltages dibutuhake dening DDR3 liwat TI kang TPS51200. Sumber daya 1.8V MGTAVTT lan MGTAVCC kanggo transceiver GTP digawe dening chip TPS74801 TI. Fungsi saben distribusi daya ditampilake ing tabel ing ngisor iki:

| Power Supply | Fungsi |

| +1.0V | FPGA inti Voltage |

| +1.8V | FPGA tambahan voltage, TPS74801 sumber daya |

| +3.3V | VCCIO saka Bank0, Bank13 lan Bank14 saka FPGA, QSIP FLASH, Clock Crystal |

| +1.5V | DDR3, Bank34 lan Bank35 saka FPGA |

| VREF,VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | FPGA Bank15, Bank16 |

| MGTAVTT(+1.2V) | GTP Transceiver Bank216 saka FPGA |

| MGTVCC(+1.0V) | GTP Transceiver Bank216 saka FPGA |

Amarga sumber daya Artix-7 FPGA nduweni syarat urutan daya, ing desain sirkuit, kita wis ngrancang miturut syarat daya chip, lan daya-on yaiku 1.0V->1.8V->(1.5 V, 3.3V, VCCIO) lan 1.0V-> MGTAVCC -> MGTAVTT, desain sirkuit kanggo njamin operasi normal chip.

Sirkuit daya ing papan inti AC7A200 FPGA ditampilake ing Gambar 10-2:

Gambar 10-2: Sumber Daya ing Papan Inti FPGA AC7A200

Part 11: Ukuran Ukuran

Gambar 11-1: Papan inti FPGA AC7A200 (Ndhuwur View)

Gambar 11-2: Papan inti FPGA AC7A200 (Ngisor View)

Dokumen / Sumber Daya

|

Papan Pangembangan FPGA ALINX AC7A200 ARTIX-7 [pdf] Manual pangguna AC7A200 ARTIX-7 Papan Pengembangan FPGA, AC7A200, ARTIX-7 Papan Pengembangan FPGA, Papan Pengembangan FPGA, Papan Pengembangan, Papan |